Content

- RISC-V Datapath Overview

- H/W Elements

- Register File

- Instruction Execution

- Multiplexors

- Hardwired Control Table

- Instruction Details

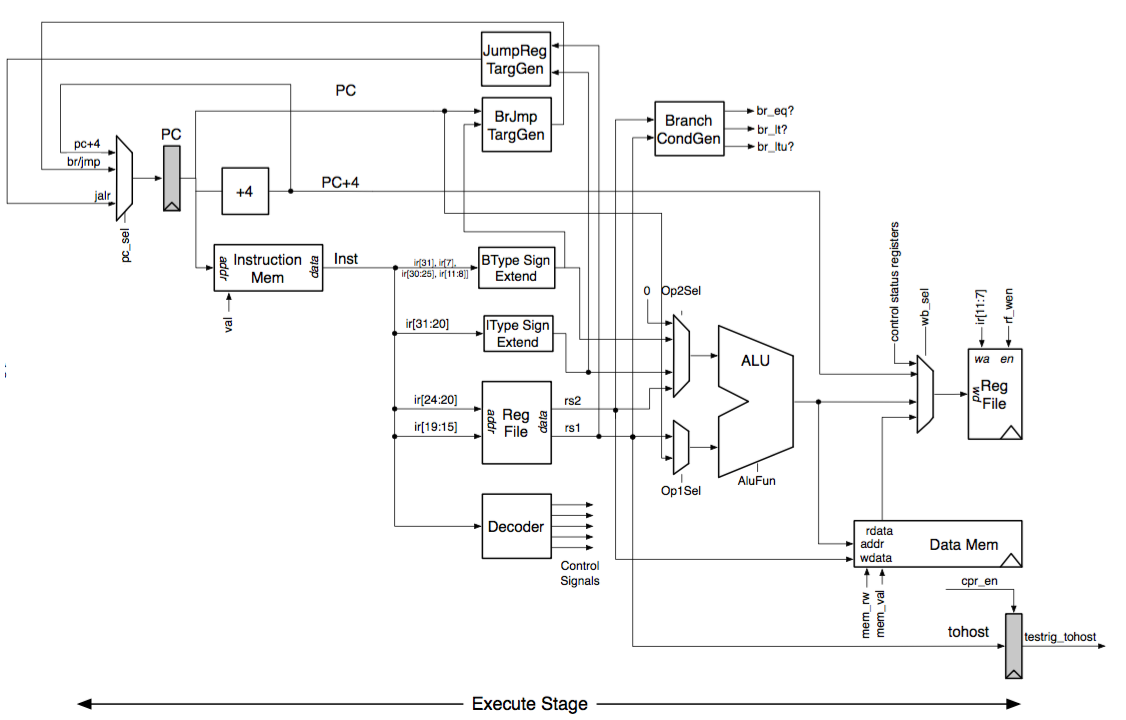

RISC-V Datapath Overview

H/W Elements

- Combinational elements: operate on data

- Input -> output

- Mux, decoder, ALU, ...

- Synchronous state elements: contain states

- >= 1 input value + clock + current state -> output

- Flip-flop, register, register file, SRAM, DRAM

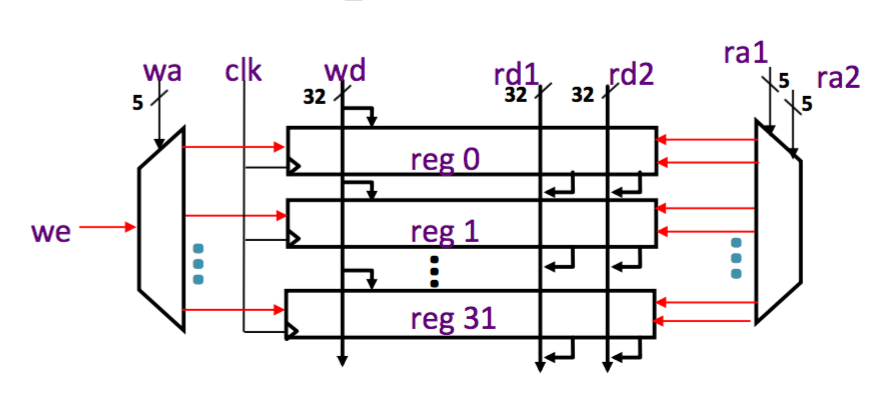

Register File

- A state element that consists of a set of registers that can be read and written by supplying a register number to be accessed

- Reads are combinational:

rd = regfile(ra)in the same cycle - Writes take place at rise of clock edge &

WE = 1 - 4 inputs (

ra1,ra2,wa,wd); 2 outputs (rd1,rd2)

Instruction Execution

- Instruction fetch

- Decode & register fetch

- ALU operation

- Memory operation (optional)

- Write back to register file (optional) + computation of next instruction address

tC > tIFetch + tRFetch + tALU+ tDMem+ tRWB

Multiplexors

- Select next PC value from PC+4, branch, or jump

- Select write data from memory rdata, ALU result, or PC+4

- Select input for ALU from register or immediate

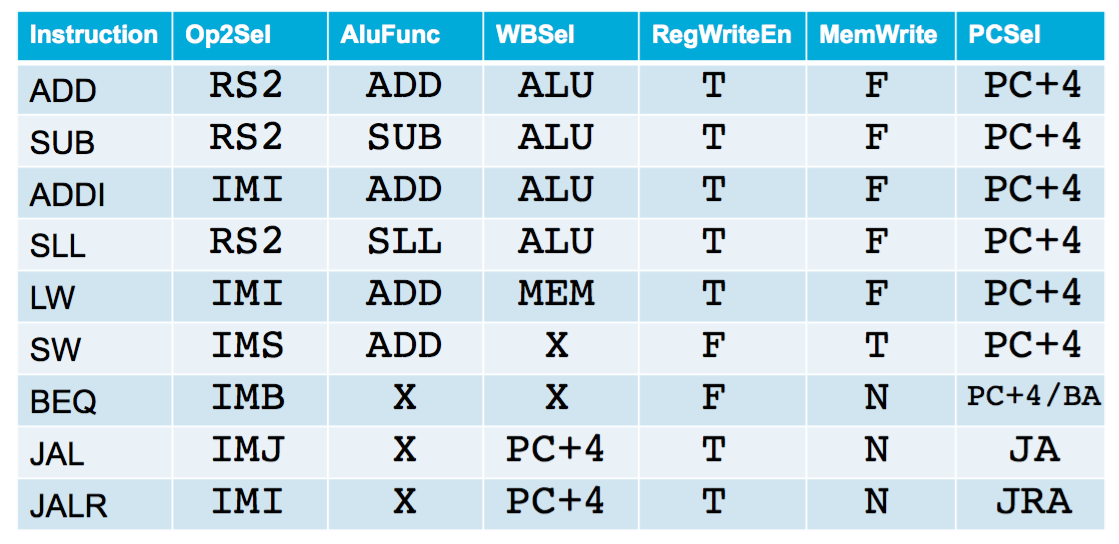

Hardwired Control Table

Instruction Details

- R-type instructions

- I-type instructions

- Sign extend immediate values

- Load/store instructions

- Sign extend offset values

- Branch instructions

- Compute branch address

- Compare register contents

- Jump instructions